Escalating Bandwidth, Thermal Constraints, and Jitter Sensitivity

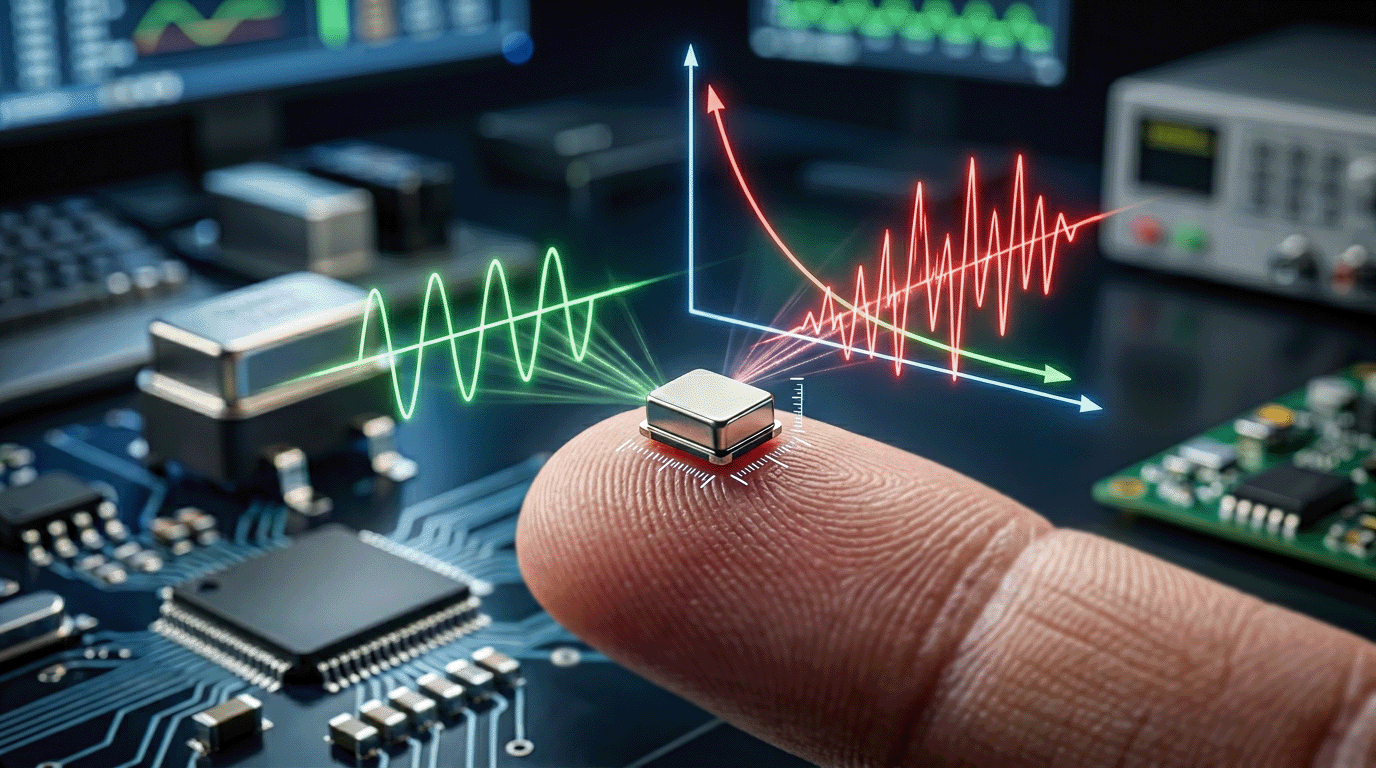

With the rapid growth of generative AI, data center traffic is exploding, pushing optical interconnect speeds from 800G toward 1.6T and 3.2T. In the Digital Signal Processors (DSPs) central to these ultra-high-speed systems, even slight timing variations during electrical-to-optical conversion accumulate as RMS jitter (phase noise). This severely degrades the Bit Error Rate (BER), making highly pure, low-jitter reference clocks more critical than ever.

At the same time, higher server density is intensifying thermal and power constraints across the data center. Within the extreme heat of optical transceivers, MEMS and PLL-based oscillators are reaching their performance limits, as temperature compensation mechanisms can introduce instability into noise characteristics. Consequently, there is an urgent need for next-generation clock solutions capable of directly generating high frequencies, such as 625 MHz, while maintaining unwavering jitter performance under severe thermal conditions.

.jpg?width=800&height=533&name=1%20Optical%20Transceivers%20(800G%20%201.6T%20%203.2T).jpg)

.jpg)